#### CZECH TECHNICAL UNIVERSITY IN PRAGUE

Faculty of Electrical Engineering Department of Electromagnetic Field

# Highly Efficient RF Power Amplifiers for Medical and Industrial Applications

DOCTORAL THESIS

Jesús Anzoátegui Cumana Morales, M.Sc.

Prague, July 2023

Ph.D Programme: P2612 Electrical Engineering and Information Technology Branch of Study: 2601V010 Radioelectronics

> Supervisor Prof. Ing. Jan Vrba, CSc. Supervisor Specialist Prof. Dr.-Ing. Jan Vrba, MSc.

The work contained in this thesis has not been previously submitted to meet requirements for an award at this or any other higher education institution. To the best of my knowledge and belief, the thesis contains no material previously published or written by another person except where due reference is made.

in Prague, .....

Jesús Anzoátegui Cumana Morales

## Acknowledgment

This thesis was written during my time as external Ph.D candidate at the Department of Electromagnetic Field, Faculty of Electrical Engineering of the Czech Technical University in Prague. Its conception would not have been possible without the assistance of many people that I would like to acknowledge.

First and foremost, I would like to thank my supervisor Prof. Ing. Jan Vrba, CSc. and supervisor specialist Prof. Dr-Ing. Jan Vrba, M.Sc. for their professional guidance, valuable comments and dedicated involvement in every step throughout the process. I would like to thank you very much for your support and understanding over the past few years.

I would like to thank the head of the Department of Electromagnetic Field, Prof. Ing. Pavel Pechač, Ph.D., for the opportunity to be an external member of this department during my doctoral studies.

My gratitude also goes to Prof. Dr. Narendra Kumar from the University of Malaya, Malaysia, for introducing me to the topic of class-E power amplifiers and for his initial support.

Special thanks to Ms Kroutilíková from the Faculty of Electrical Engineering for support and guidance on administrative issues.

I would like to acknowledge the excellent cooperation with my colleagues from the Department of Biomedical Technology at the Faculty of Biomedical Engineering in Kladno, specially Assoc. Prof. Ing. David Vrba, Ph.D., Assoc. Prof. Ing. Ondrej Fišer, Ph.D., Ing. Tomáš Pokorný, Ph.D. and Ing. Marek Novák, Ph.D. for the valuable discussions and help during my stay in Kladno. I would particularly like to thank Ing. Tomáš Dříždal, Ph.D., for preparing the agar phantoms and for supporting me with the RF heating experiments as well as for sharing his insights and knowledge in the area of RF hyperthermia.

My gratitude also goes to Yury Abramov, M.Sc., my previous and long-time manager at Corning Optical Communications GmbH & Co. KG, for his support and encouragement.

Last but not least, I would like to thank my family: my mother, brother and sister as well as to my Polish family for their constant encouragement. I would also like to thank my wife Hanna and my daughter Carmen Sophia for their love, inspiration, understanding and patience during the time I was working on my Ph.D thesis.

### Abstract

Cutting down energy consumption in electronic systems is required to increase operating time in battery-powered products, to reduce size and weight by alleviating cooling requirements and is essential to reduce carbon dioxide emissions. Since power amplifiers are among the power hungriest components in an RF transmitting system, improving their efficiency is essential to reduce overall power consumption.

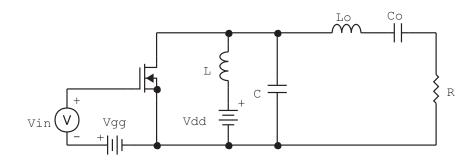

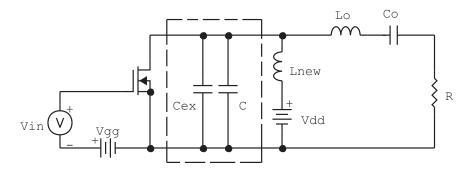

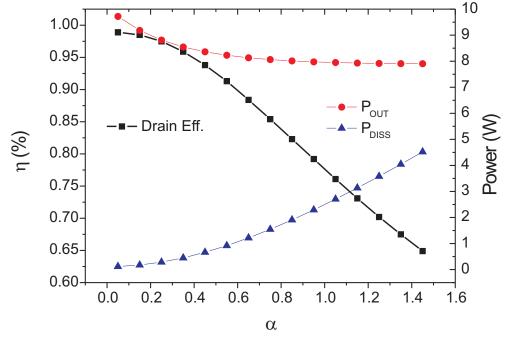

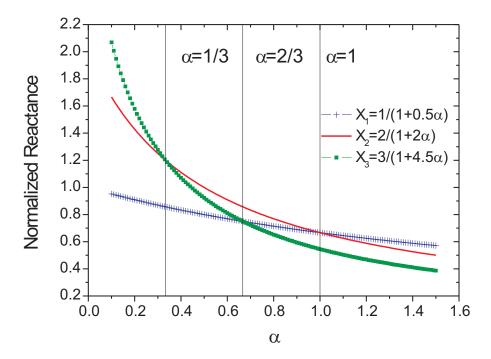

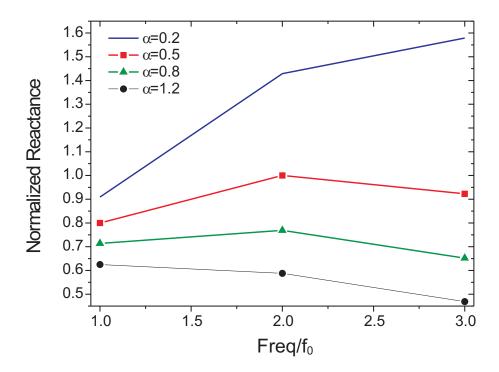

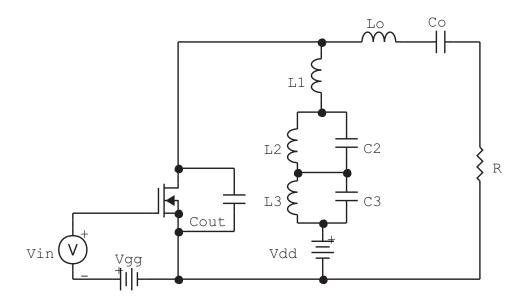

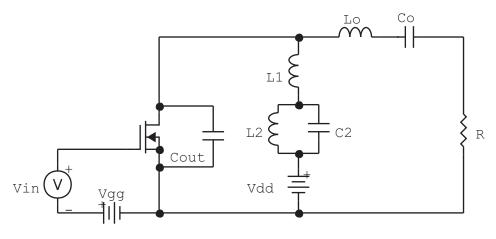

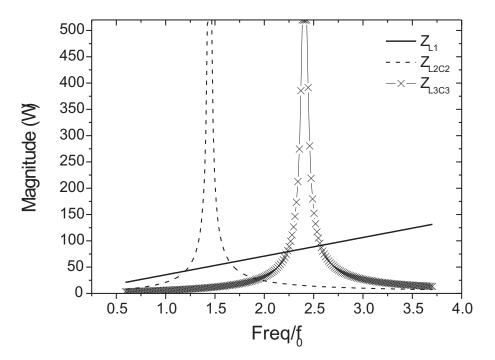

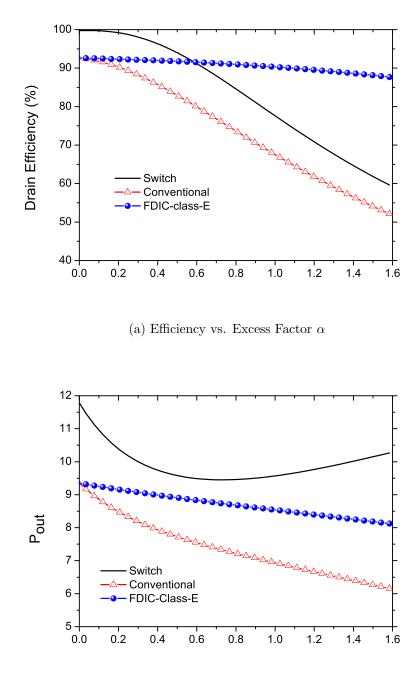

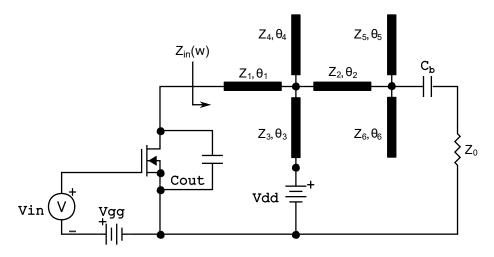

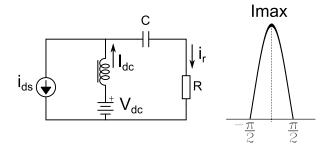

This thesis studies the class-E power amplifier, a high-efficiency amplifying concept, in which the active device behaves like a switching element. Applications like RF heating in which linearity is not a demanding requirement, can resort to this kind of concept. It has been shown that excessive transistor output capacitance degrades performance in this amplifier class, reducing efficiency and limiting its highest frequency of operation. In this thesis, a new circuit topology is proposed to accommodate devices with excessive output capacitance, thereby improving efficiency and extending maximum frequency of operation. The proposed topology, composed of an inductor in series with sub-harmonic resonators, replaces the DC feed inductor in the classical finite-feed class-E amplifier circuit. In this way, output capacitance compensation is achieved. The corresponding theory and design equations are developed in this work. To validate the proposed concepts, a circuit demonstrator has been designed, built and measured.

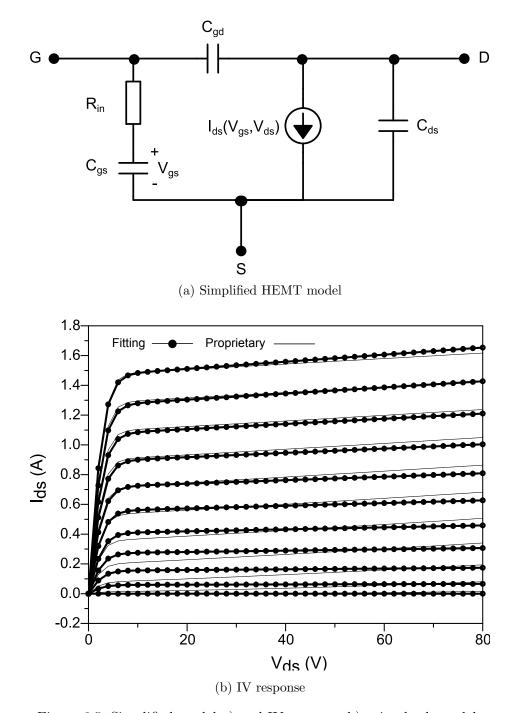

This compensating approach, which is called Frequency-Dependent Inductive Compensation (FDIC) in this thesis, is further evaluated to understand its validity at microwaves. After extracting a simplified large-signal model of a GaN HEMT, extensive simulations are used to evaluate the impact of excessive transistor output capacitance on class-E. This approach removes the main idealization when analyzing this amplifier class, i.e., the switch is replaced by a voltage-controlled current source. Using the extracted model instead of the ideal switch, allows us to evaluate the effects of non-ideal switching, intrinsic capacitance voltage-dependency, feedback capacitance and saturation resistance. The effect of the FDIC on the transistor drain voltage and current waveforms in the class-E topology is studied and the limitations of this approach are discussed. Once more, a circuit demonstrator is designed and built to validate the study.

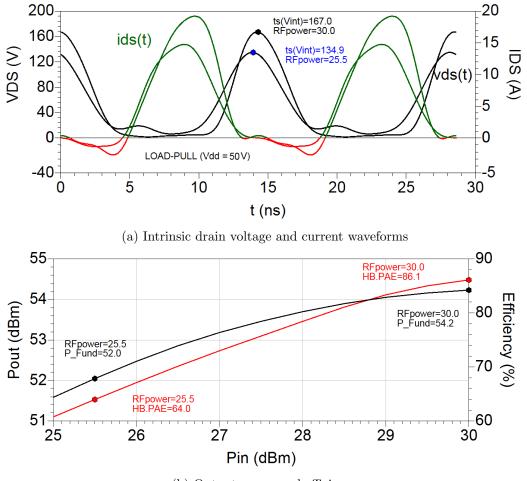

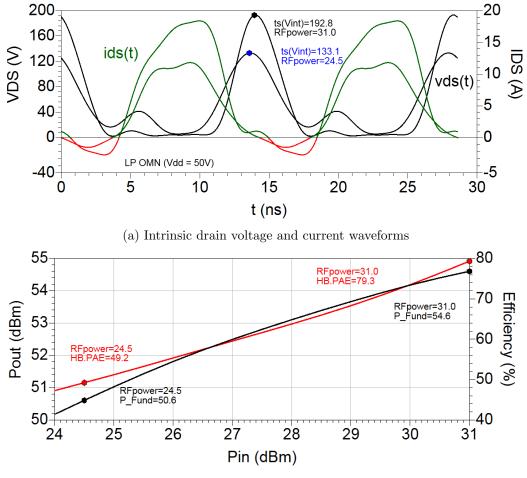

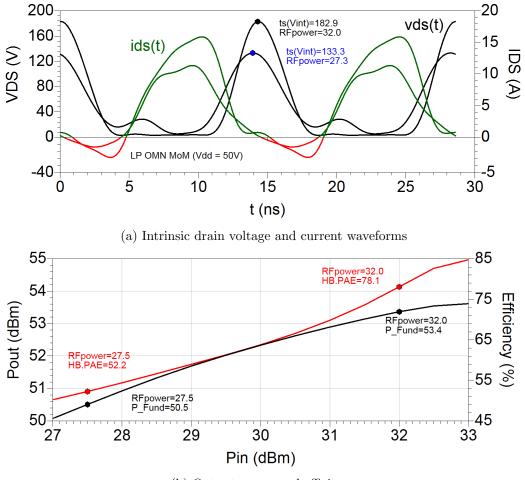

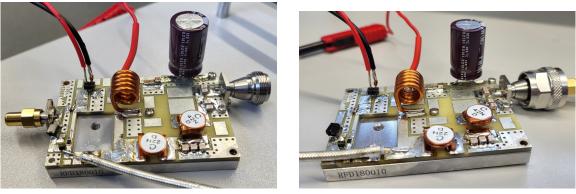

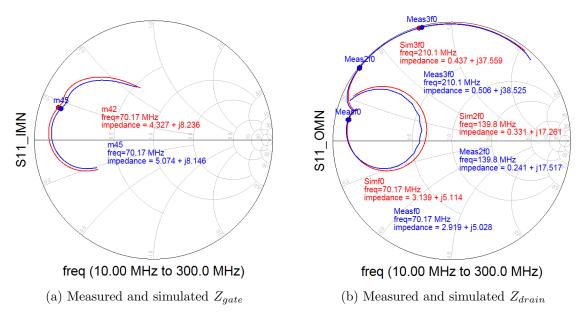

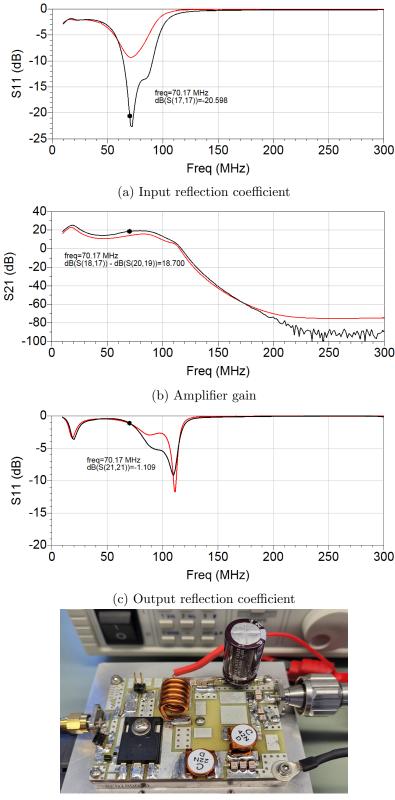

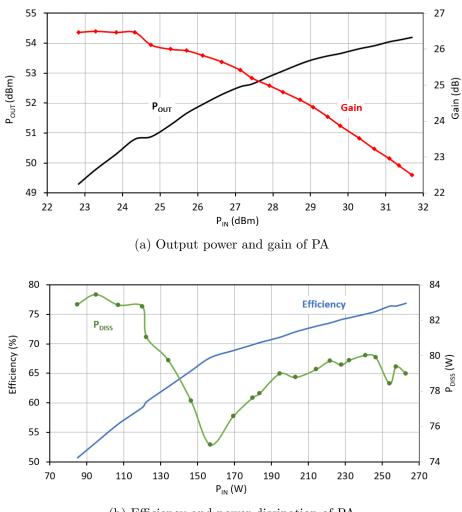

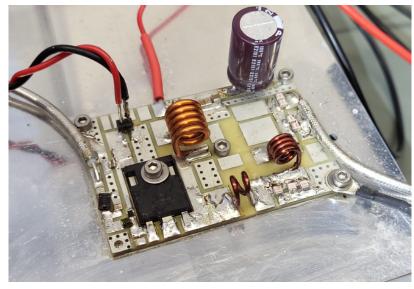

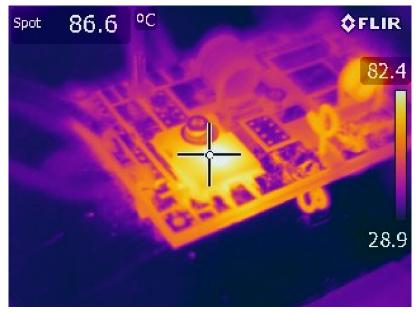

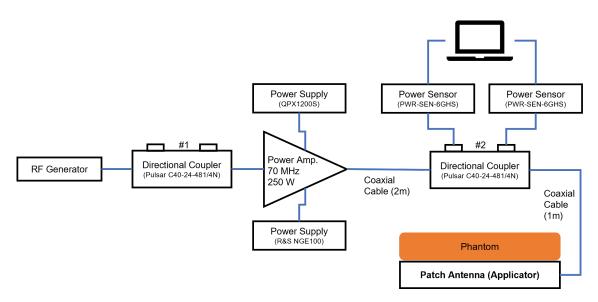

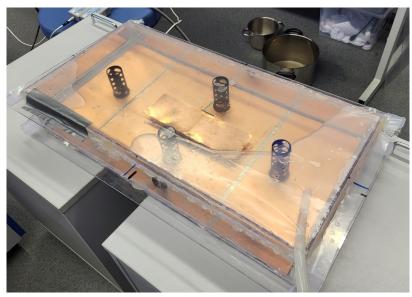

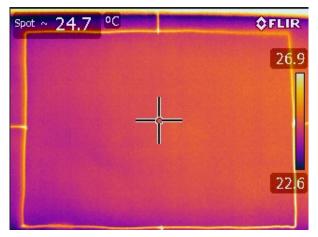

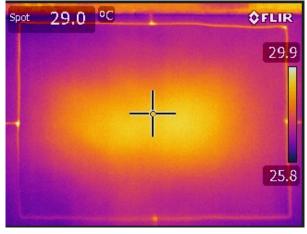

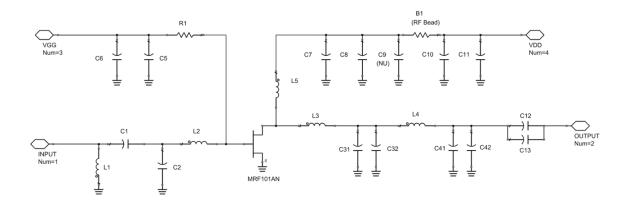

The final part of the thesis addresses power amplifiers for hyperthermia systems. A 250 W amplifier prototype operating at 70 MHz for regional hyperthemia is designed and built. In this case, two design approaches are studied, namely, using the conventional class-E design method based on existing equations, and secondly, by performing load-pull simulations using the available large-signal model of the LDMOS device. The intrinsic drain current and voltage waveforms are used to guide the design process and to optimize efficiency. Finally, RF heating experiments using an agar phantom are performed to evaluate the amplifier when delivering power under close-to-real conditions.

## Abstrakt

Snížení spotřeby energie v elektronických systémech je nutné ke zvýšení provozní doby u produktů napájených bateriemi, ke snížení velikosti a hmotnosti snížením požadavků na chlazení a je nezbytné pro snížení emisí oxidu uhličitého. Vzhledem k tomu, že výkonové zesilovače patří mezi energeticky nejnáročnější komponenty ve vysokofrekvenčním vysílacím systému, zlepšení jejich účinnosti je zásadní pro snížení celkové spotřeby energie.

Tato práce studuje výkonový zesilovač třídy E, koncept vysoce účinného zesilovače, ve kterém se aktivní zařízení chová jako spínací prvek. Tento druh konceptu mohou využít aplikace, jako je vysokofrekvenční ohřev, pro kterou linearita nepatří mezi kritické parametrem. Bylo prokázáno, že nadměrná výstupní kapacita tranzistoru snižuje výkon v této třídě zesilovačů, snižuje účinnost a omezuje jeho nejvyšší provozní frekvenci.

V této práci je navržena nová obvodová topologie pro umístění zařízení s nadměrnou výstupní kapacitou, čímž se zvýší účinnost a prodlouží maximální frekvence provozu. Navrhovaná topologie, složená z induktoru v sérii se subharmonickými rezonátory, nahrazuje stejnosměrný napájecí induktor v klasickém obvodu zesilovače třídy E.

Tímto způsobem je dosaženo kompenzace výstupní kapacity. V této práci jsou vyvinuty odpovídající teorie a návrhové rovnice. Pro ověření navržených konceptů byl navržen, postaven a změřen obvodový demonstrátor. Tento kompenzační přístup, který se v této práci nazývá frekvenčně závislá indukční kompenzace - FDIC (Frequency-Dependent Inductive Compensation), je dále hodnocen, tak aby byla pochopena jeho platnost ve spodní části mikrovlnného spektra.

Po extrahování zjednodušeného modelu GaN HEMT pro velké signály jsou využity rozsáhlé simulace k vyhodnocení dopadu nadměrné výstupní kapacity tranzistoru na třídu E. Tento přístup odstraňuje hlavní idealizaci při analýze této třídy zesilovačů, tedy, že přepínač je nahrazen napěťově řízeným zdrojem proudu. Použití extrahovaného modelu místo ideálního spínače nám umožňuje vyhodnotit účinky neideálního spínání, vlastní kapacitní závislost na napětí, zpětnovazební kapacity a saturačního odporu. Je studován vliv FDIC na průběhy napětí a proudu tranzistoru v topologii třídy E a jsou diskutována omezení tohoto přístupu. Ještě jednou je navržen a postaven demonstrátor obvodu pro ověření studie.

Závěrečná část práce se zabývá výkonovými zesilovači pro hypertermické systémy. Je navržen a postaven prototyp 250 W zesilovače pracujícího na frekvenci 70 MHz pro regionální hypertemii. V tomto případě jsou studovány dva přístupy k návrhu, a to pomocí konvenční metody návrhu třídy E založené na existujících rovnicích a za druhé pomocí load-pull simulací s využitím dostupného modelu zařízení LDMOS pro velký signál. Vlastní průběhy proudu a napětí se používají k vedení procesu návrhu a k optimalizaci účinnosti.

Nakonec se provádějí experimenty s vysokofrekvenčním ohřevem s použitím agarového fantomu, aby se vyhodnotil zesilovač při dodávání energie za podmínek blízkých reálným.

## Keywords

power amplifier, class E amplifier, class J amplifier, switched mode amplifier, high efficiency, excess capacitance, inductive compensation, GaN HEMT, LDMOS, hyperthermia, agar phantom

## Klíčová slova

výkonový zesilovač, zesilovač třídy E, zesilovač třídy J, spínaný zesilovač, vysoká účinnost, nadměrná kapacita, indukční kompenzace, GaN HEMT, LDMOS, hypertermie, agarový fantom

# Contents

| Lis | t of              | Figures                                                     | xv            |

|-----|-------------------|-------------------------------------------------------------|---------------|

| Lis | t of <sup>·</sup> | Tables                                                      | xix           |

| Lis | t of <i>i</i>     | Acronyms                                                    | xxi           |

| 1   | Intro<br>1.1      | D <b>duction</b><br>Motivation                              | <b>1</b><br>1 |

| 2   | RF I              | Power Amplifier Fundamentals                                | 5             |

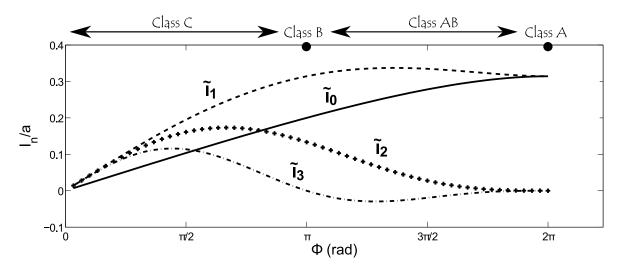

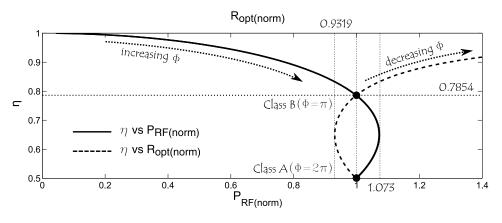

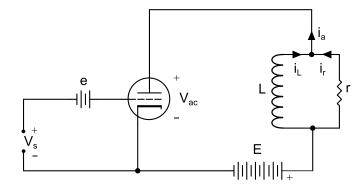

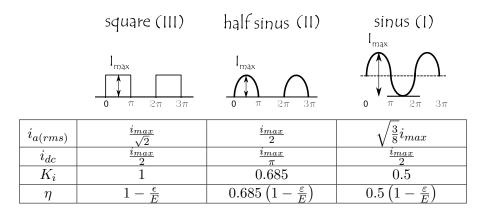

|     | 2.1               | Conventional Power Amplifiers                               | 5             |

|     |                   | 2.1.1 Generalized Analysis of Conventional Power Amplifiers | 6             |

|     | 2.2               | High Efficiency Amplifier Concepts                          | 10            |

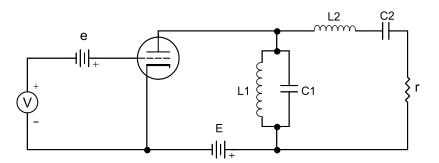

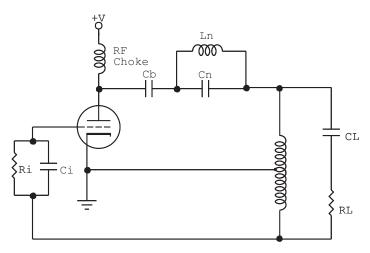

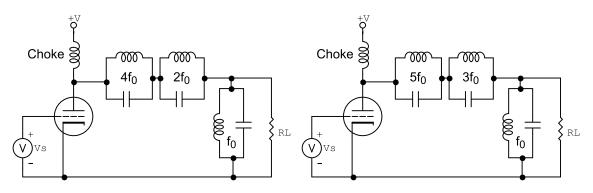

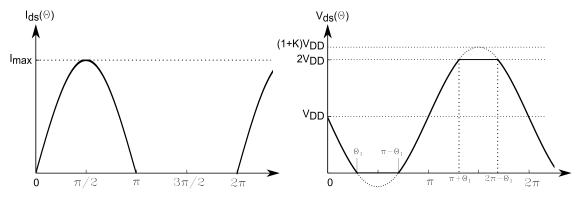

|     |                   | 2.2.1 Polyharmonic Approaches and Early Concepts            | 10            |

|     |                   | 2.2.2 Overdriven Power Amplifiers                           | 14            |

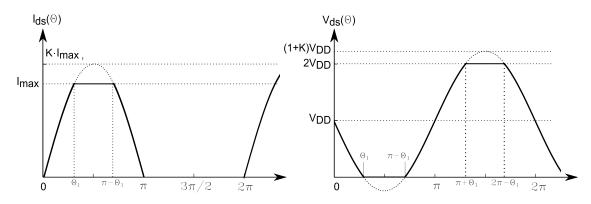

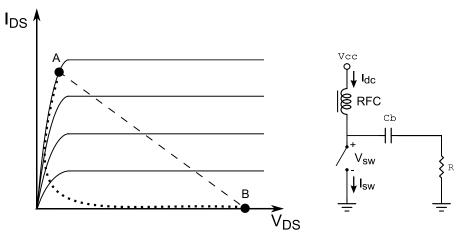

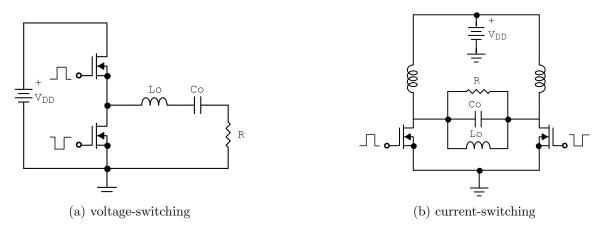

|     |                   | 2.2.3 Switched-Mode Power Amplifiers                        | 18            |

| 3   | Stat              | e of the Art on Class-E Power Amplifiers                    | 21            |

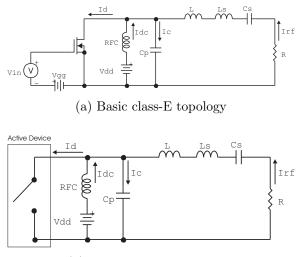

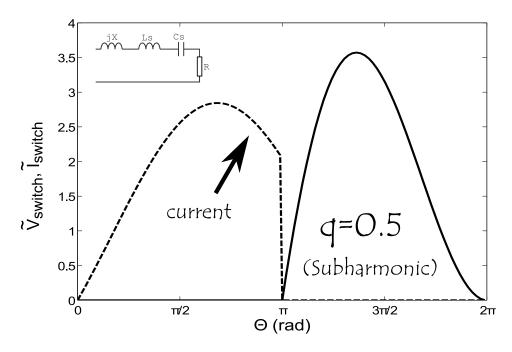

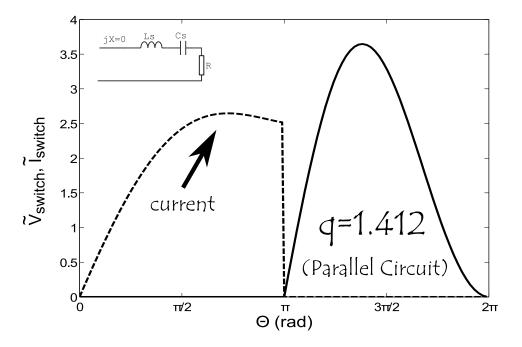

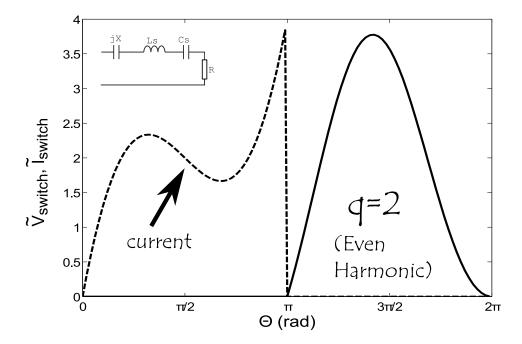

|     | 3.1               | Low-Frequency Analysis of Class-E Power Amplifiers          | 21            |

|     |                   | 3.1.1 Shunt Capacitor Class-E Analysis                      | 23            |

|     |                   | 3.1.2 Frequency limitation in class-E                       | 30            |

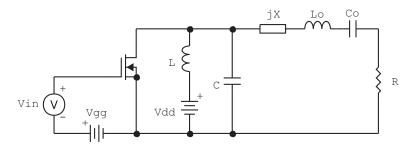

|     |                   | 3.1.3 Class-E with finite-feed inductance                   | 31            |

|     | 3.2               | High-Frequency Analysis of Class-E Power Amplifiers         | 34            |

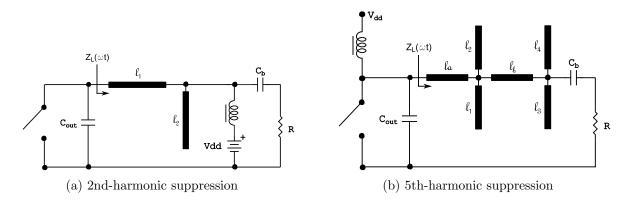

|     |                   | 3.2.1 Harmonic Suppression Network Approach                 | 34            |

|     |                   | 3.2.2 Mutiharmonic Load Network Synthesis                   | 37            |

| 4   | Aim               | of the Dissertation Thesis                                  | 41            |

|     | 4.1               | Outline                                                     | 41            |

| 5   | New               | Topologies of Class-E Power Amplifiers                      | 43            |

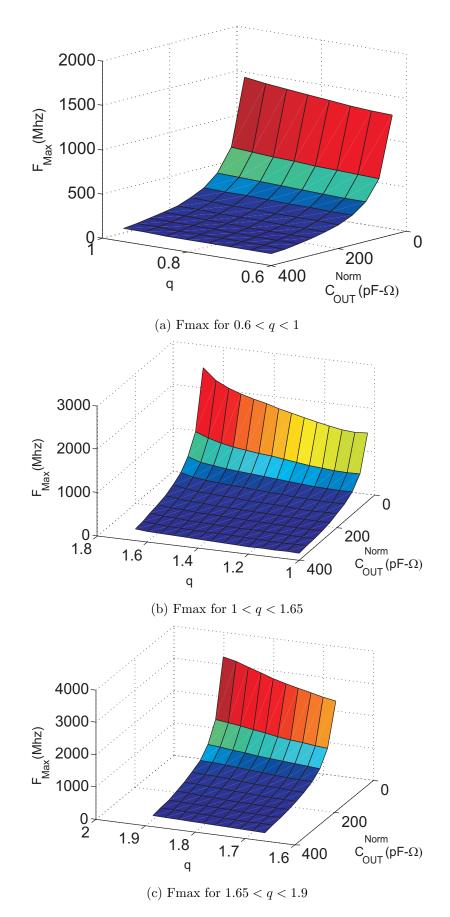

|     | 5.1               | Class-E with finite DC feed Inductance                      | 43            |

|     |                   | 5.1.1 Simplified Analysis                                   | 43            |

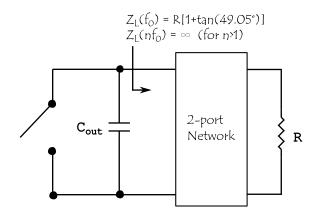

|     |                   | 5.1.2 Frequency-Domain Analysis of Parallel-Circuit Class-E | 45            |

|     | 5.2               | Lumped Equivalent Circuit of New Inductor                   | 50            |

|     | 5.3               | Simulations and Measurements                                | 54            |

| 6   | Indu              | ctive Compensated Microwave Class-E Power Amplifier         | 63            |

|     | 6.1               | Review of FDIC                                              | 64            |

|     |                   | 6.1.1 General Concept                                       | 64            |

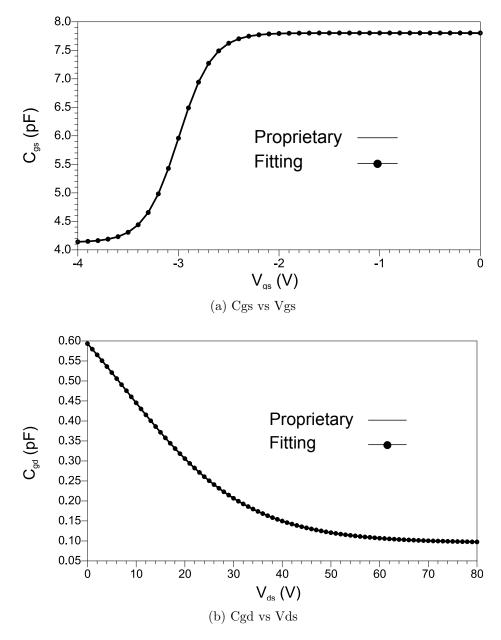

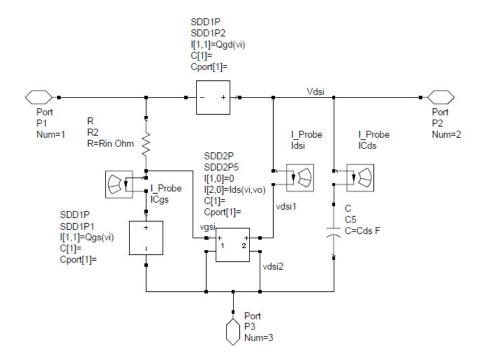

| 6.2       FDIC Evaluation using Transistor Model         6.2.1       Extraction of compact HEMT Model         6.2.2       Simulation of conventional Class-E using SDD Model         6.3.3       General Approach to Design FDIC-Class-E         6.3.1       Impedances for FDIC and Class-E Network         6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Dewer Amplifier Mither for Regional Hyperthermia         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       Efficiency is for two-resonator network         .2       Equations for two-resonator network         .3       BOM Gain block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  | 65  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|

| 6.2.2       Simulation of conventional Class-E using SDD Model         6.2.3       Simulation of FDIC-Class-E using SDD Model         6.3       General Approach to Design FDIC-Class-E         6.3.1       Impedances for FDIC and Class-E Network         6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Design of 100 W Amplifier for Regional Hyperthermia         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       Efficiency for two-resonator network         .2       Equations for two-resonator network         .3       BOM Gain block         .4       BOM Gain block <t< td=""><td></td><td>68</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 68  |

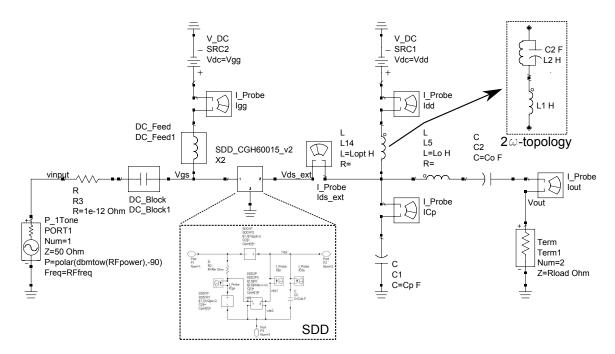

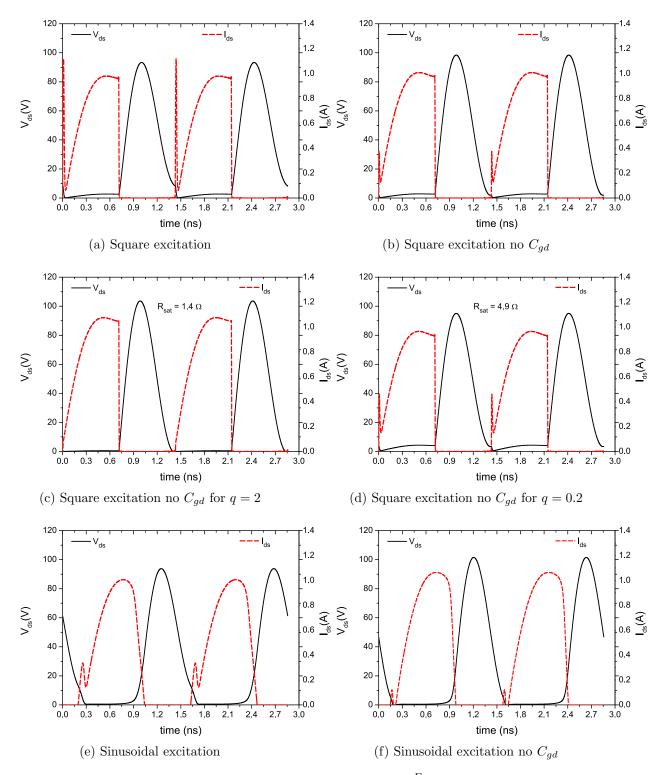

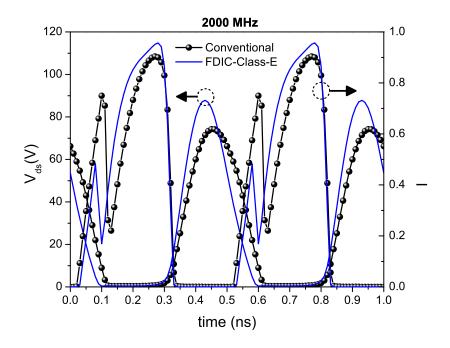

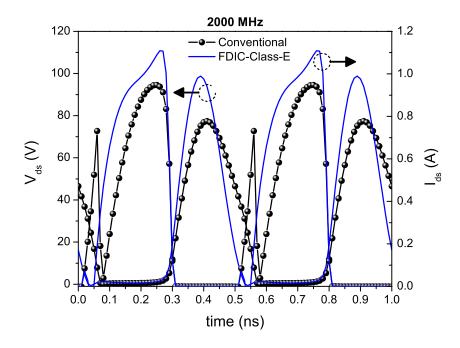

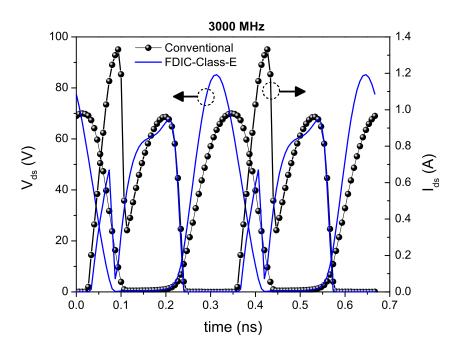

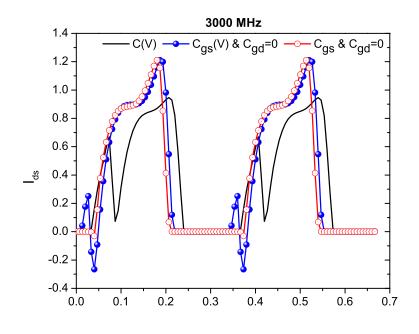

| 6.2.3       Simulation of FDIC-Class-E using SDD Model         6.3       General Approach to Design FDIC-Class-E         6.3.1       Impedances for FDIC and Class-E Network         6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Dewer Amplifier implementation and Measurements         7.2.2       Power Amplifier implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .1       System of two-resonator network         .2       Equations for two-resonator network         .3       BOM Gain block <tr< td=""><td></td><td>68</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | 68  |

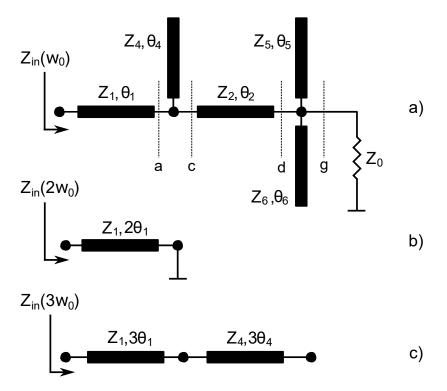

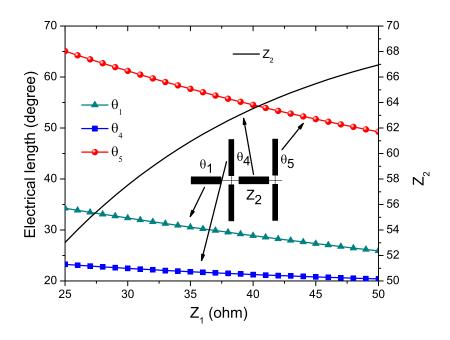

| 6.3       General Approach to Design FDIC-Class-E         6.3.1       Impedances for FDIC and Class-E Network         6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .1       System of two-resonator network         .2       Equations for two-resonator network         .3       BOM Pre-Driver         .3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  | 72  |

| 6.3.1       Impedances for FDIC and Class-E Network         6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.1       Power Amplifiers for RF Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3       Power Amplifier Implementation         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .1       System of two-resonator network         .2       Equations for two-resonator network         .3       BOM Pre-Driver         .3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  | 74  |

| 6.3.2       Simulations using SDD and Commercial Model         6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2       Design onsiderations and Driver requirements         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .2       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block <t< td=""><td></td><td>77</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  | 77  |

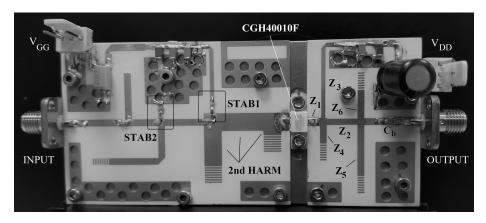

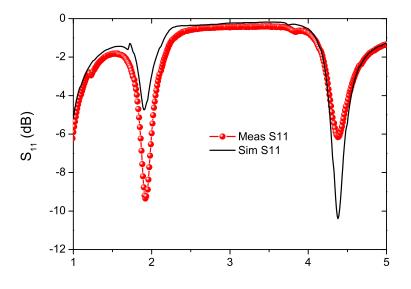

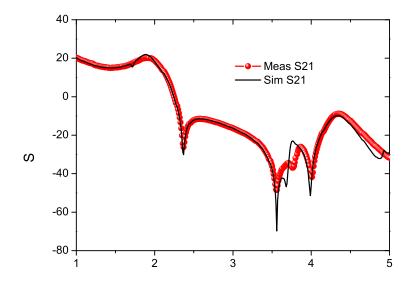

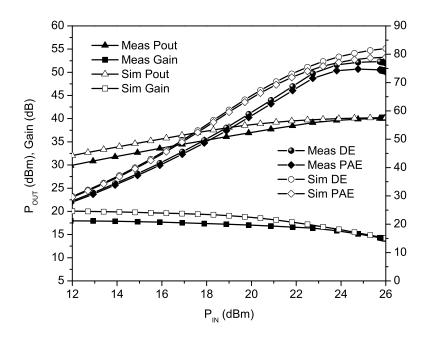

| 6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.1       Power Amplifiers for RF Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2       Design considerations and Driver requirements         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of two-resonator network         .2       Equations for two-resonator network         .2       Equations for two-resonator network for variable $q$ .1       BOM Gain block         .2       BOM Freadate         .3       BOM Fin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  | 79  |

| 6.4       Implementation and Experimental Results         7       Power Amplifiers for Hyperthermia Systems         7.1       Overview of Radio Frequency Hyperthermia         7.1       Power Amplifiers for RF Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2       Design considerations and Driver requirements         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of two-resonator network         .2       Equations for two-resonator network         .2       Equations for two-resonator network for variable $q$ .1       BOM Gain block         .2       BOM Freadate         .3       BOM Fin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  | 81  |

| 7.1       Overview of Radio Frequency Hyperthermia       7.1.1         7.1       Power Amplifiers for RF Hyperthermia       7.1.1         7.2       Design of 100 W Amplifier for Regional Hyperthermia       7.2.1         7.2       Design considerations and Driver requirements       7.2.1         7.2       Power Amplifier Implementation and Measurements       7.2.2         7.3       Power Amplifier Implementation and Measurements       7.3.1         7.3.1       Evaluation of PC Class-E Topology via Simulations       7.3.2         7.3.2       General Approach via Load-Pull Simulations       7.3.3         7.3.3       Power Amplifier Implementation       7.3.4         7.3.4       Experiments using Agar Phantom       7.3.4         8       Conclusions and Outlook       Bibliography         Appendix A       .1       Efficiency in class-B PA with resistive load       .1         .1       Efficiency for two-resonator network       .1       .1         Appendix B       .1       System of Equations for Finite Feed Class E       .1         .1       Equations for two-resonator network       .1       .1         .2       Equations for two-resonator network       .2       .1         .2       Equations for L <sub>1</sub> L <sub>2</sub> C <sub>2</sub> network for variable $q$ <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |     |

| 7.1       Overview of Radio Frequency Hyperthermia       7.1.1         7.1       Power Amplifiers for RF Hyperthermia       7.1.1         7.2       Design of 100 W Amplifier for Regional Hyperthermia       7.2.1         7.2       Design considerations and Driver requirements       7.2.1         7.2       Power Amplifier Implementation and Measurements       7.2.2         7.3       Power Amplifier Implementation and Measurements       7.3.1         7.3.1       Evaluation of PC Class-E Topology via Simulations       7.3.2         7.3.2       General Approach via Load-Pull Simulations       7.3.3         7.3.3       Power Amplifier Implementation       7.3.4         7.3.4       Experiments using Agar Phantom       7.3.4         8       Conclusions and Outlook       Bibliography         Appendix A       .1       Efficiency in class-B PA with resistive load       .1         .1       Efficiency for two-resonator network       .1       .1         Appendix B       .1       System of Equations for Finite Feed Class E       .1         .1       Equations for two-resonator network       .1       .1         .2       Equations for two-resonator network       .2       .1         .2       Equations for L <sub>1</sub> L <sub>2</sub> C <sub>2</sub> network for variable $q$ <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  | 91  |

| 7.1.1       Power Amplifiers for RF Hyperthermia         7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.1       Design considerations and Driver requirements         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3       Power Amplifier With $P_0 = 250$ W         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .2       Equations for two-resonator network         .2       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .3       BOM Gain block         .2       BOM Final Stage         .3       BOM Final Stage         .1       Equivalent output circuit of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  | 91  |

| 7.2       Design of 100 W Amplifier for Regional Hyperthermia         7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3       Power Amplifier with $P_0 = 250$ W         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         7.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.1       Efficiency in class-B PA with resistive load         7.1       Equations for two-resonator network         7.2       Equations for two-resonator network         7.3       Equations for $L_1L_2C_2$ network for variable $q$ 7.4       BOM Gain block         7.5       BOM F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |     |

| 7.2.1       Design considerations and Driver requirements         7.2.2       Power Amplifier Implementation and Measurements         7.3       Power Amplifier with $P_0 = 250$ W         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography       Appendix A         .1       Efficiency in class-B PA with resistive load         .1       System of Equations for Finite Feed Class E         .1       System of Equations for Finite Feed Class E         .2       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |     |

| 7.2.2       Power Amplifier Implementation and Measurements         7.3       Power Amplifier with $P_0 = 250$ W         7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography         Appendix A         .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |     |

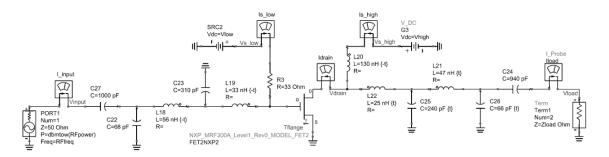

| 7.3       Power Amplifier with $P_0 = 250$ W       7.3.1         For the experiment of the probability of th |  |     |

| 7.3.1       Evaluation of PC Class-E Topology via Simulations         7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography         Appendix A         .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for two-resonator network for variable $q$ .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |     |

| 7.3.2       General Approach via Load-Pull Simulations         7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography         Appendix A         .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for L <sub>1</sub> L <sub>2</sub> C <sub>2</sub> network for variable q         .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |     |

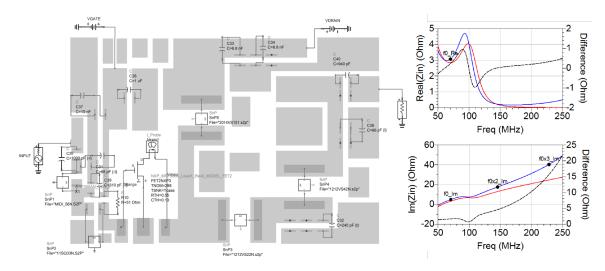

| 7.3.3       Power Amplifier Implementation         7.3.4       Experiments using Agar Phantom         8       Conclusions and Outlook         Bibliography         Appendix A         .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .3       BOM Gain block         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |     |

| 7.3.4 Experiments using Agar Phantom         8 Conclusions and Outlook         Bibliography         Appendix A         .1 Efficiency in class-B PA with resistive load         Appendix B         .1 System of Equations for Finite Feed Class E         Appendix C         .1 Equations for two-resonator network         .2 Equations for $L_1L_2C_2$ network for variable $q$ .3 BOM Gain block         .2 BOM Pre-Driver         .3 BOM Final Stage         .1 Equivalent output circuit of MRF300AN and intrinsic waveforms         .1 Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |     |

| <ul> <li>8 Conclusions and Outlook</li> <li>Bibliography</li> <li>Appendix A <ol> <li>Efficiency in class-B PA with resistive load</li> <li>Appendix B <ol> <li>System of Equations for Finite Feed Class E</li> </ol> </li> <li>Appendix C <ol> <li>Equations for two-resonator network</li> <li>Equations for L<sub>1</sub>L<sub>2</sub>C<sub>2</sub> network for variable q</li> </ol> </li> <li>Appendix D <ol> <li>BOM Gain block</li> <li>BOM Pre-Driver</li> <li>BOM Final Stage</li> </ol> </li> <li>Appendix E <ol> <li>Equivalent output circuit of MRF300AN and intrinsic waveforms</li> </ol> </li> </ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |     |

| Bibliography         Appendix A         .1       Efficiency in class-B PA with resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  | 119 |

| Appendix A         .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |     |

| .1       Efficiency in class-B PA with resistive load         Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | 123 |

| Appendix B         .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Fre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | 135 |

| .1       System of Equations for Finite Feed Class E         Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ .2       Equations for $L_1L_2C_2$ network for variable $q$ .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  | 135 |

| Appendix C         .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ Appendix D         .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | 137 |

| .1       Equations for two-resonator network         .2       Equations for $L_1L_2C_2$ network for variable $q$ Appendix D         .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 137 |

| .2       Equations for $L_1L_2C_2$ network for variable $q$ .         Appendix D         .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .4       Equivalent output circuit of MRF300AN and intrinsic waveforms         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  | 139 |

| Appendix D         .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | 139 |

| .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .3       BOM Final Stage         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | 139 |

| .1       BOM Gain block         .2       BOM Pre-Driver         .3       BOM Final Stage         .3       BOM Final Stage         Appendix E         .1       Equivalent output circuit of MRF300AN and intrinsic waveforms         Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | 141 |

| <ul> <li>.2 BOM Pre-Driver</li> <li>.3 BOM Final Stage</li> <li>Appendix E</li> <li>.1 Equivalent output circuit of MRF300AN and intrinsic waveforms</li> <li></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 141 |

| Appendix E<br>.1 Equivalent output circuit of MRF300AN and intrinsic waveforms<br>Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  | 141 |